#### © Eric A. Durant, PhD

### © Eric A. Durant, PhD

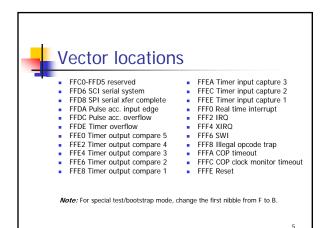

| Jump vectors, standard ROMs<br>(1/2) |         |                              |   |  |  |

|--------------------------------------|---------|------------------------------|---|--|--|

|                                      | Address | Vector                       |   |  |  |

|                                      | 00C4    | SCI                          |   |  |  |

|                                      | 00C7    | SPI                          |   |  |  |

|                                      | 00CA    | Pulse Accumulator Input Edge |   |  |  |

|                                      | 00CD    | Pulse Accumulator Overflow   |   |  |  |

|                                      | 00D0    | Timer Overflow               |   |  |  |

|                                      | 00D3    | Timer Output Compare 5       |   |  |  |

|                                      | 00D6    | Timer Output Compare 4       |   |  |  |

|                                      | 00D9    | Timer Output Compare 3       |   |  |  |

|                                      | 00DC    | Timer Output Compare 2       |   |  |  |

|                                      | 00DF    | Timer Output Compare 1       |   |  |  |

|                                      |         |                              | 7 |  |  |

| Jur<br>(2/ |      | ctors, standard RC    | OMs |

|------------|------|-----------------------|-----|

|            | 00E2 | Timer Input Capture 3 |     |

|            | 00E5 | Timer Input Capture 2 |     |

|            | 00E8 | Timer Input Capture 1 |     |

|            | 00EB | Real Time Interrupt   |     |

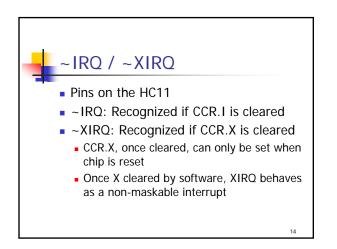

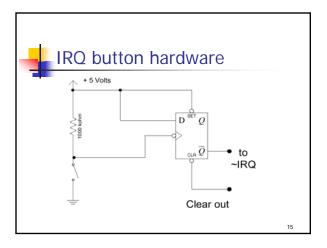

|            | 00EE | IRQ                   |     |

|            | 00F1 | XIRQ                  |     |

|            | 00F4 | SWI                   |     |

|            | 00F7 | Illegal Opcode        |     |

|            | 00FA | COP Fail              |     |

|            | 00FD | Clock Monitor         |     |

|            |      |                       | 8   |

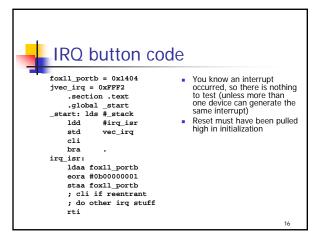

| <pre>op_jmp_ext = 0x7E ; opcode of the JMP<br/>; (extended mode) instruction<br/>jvec_irq = 0xEE ; location of RAM jump vector<br/>; (external interrupt request)</pre> |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <pre>; set up JMP vector<br/>ldaa #op_jmp_ext<br/>staa *jvec_irq<br/>ldd #irq_isr ; address of the ISR to<br/>; follow the JMP opcode<br/>std *jvec_irq+1</pre>         |   |

|                                                                                                                                                                         | 9 |

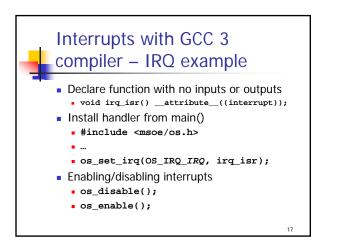

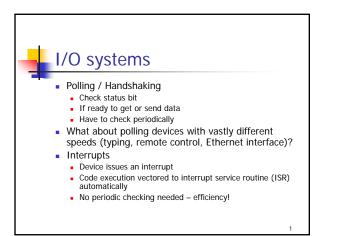

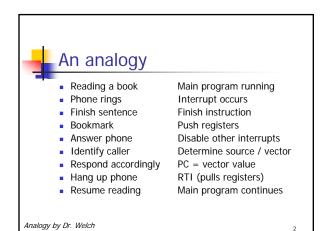

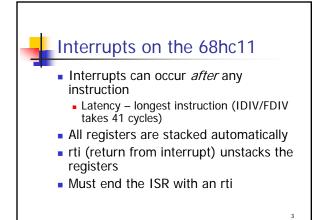

## How do you turn on interrupts?

- Interrupts above IRQ in the previous tables are turned on/off by I bit in CCR

- CLI allows interrupts to occur

- SEI turns off interrupts

- I bit set during an interrupt so the interrupt does not interrupt itself

# Interrupts – subsystem-

- Most HC11 subsystems (*e.g.*, timers) require additional handling

- Initialization: set interrupt enable bit

- Processing complete flag (tell subsystem to go on to next sample, etc.)

# SWI – software interrupt

- Instruction that triggers an interrupt

- Uses...

- Test portions of an ISR for hardware that isn't ready yet → install its vector in the SWI vector and write a test program

- Convenience like a subroutine that automatically preserves caller's registers (takes time, but not extra code)...

- Note: often used by debuggers and talkers

12

10

11

| 5       | SWI example                 |                            |    |

|---------|-----------------------------|----------------------------|----|

| vec_swi | = 0xFFF6<br>.section .text  | swi_isr:<br>; no push/pull |    |

|         | .global _start              | ; do subroutine stuff      |    |

|         |                             | rti ; (not rts)            |    |

| _start: | lds #_stack                 |                            |    |

|         | ldd #swi_isr<br>std vec_swi |                            |    |

|         | cli                         |                            |    |

| again:  | swi<br>bra again            |                            |    |

|         |                             |                            | 13 |